# Analysis and Simulation of Seven Level Inverter System

G. Mahesh Manivanna<sup>1</sup>, S. Rama Reddy<sup>2</sup>

<sup>1</sup>Sathyabama University, Tamil Nadu, India

<sup>2</sup>Jerusalem College of Engineering, Tamil Nadu, India

## Abstract

This paper deals with the analysis and simulation of the seven level inverter. This paper presents the seven level inverter with harmonics reduction along with the reduction. The percentage (%) total harmonic distortion is calculated for seven level inverter. The harmonic reduction is achieved by selecting appropriate switching angles. The functionality verification of the seven level inverter is done using MATLAB.

Key words: Neutral point clamped inverter, cascaded multi level inverter.

## I. INTRODUCTION

The multi level inverter was first introduced in 1975. The three level converters was the first multi level inverter introduced. A multilevel converter is a power electronic system that synthesizes a desired output voltage from several levels of dc voltages as inputs. With an increasing number of dc voltage sources, the converter output voltage waveform approaches a nearly sinusoidal waveform while using a fundamental frequency-switching scheme. The primary advantage of multi level inverter is their small output voltage, results in higher output quality, lower harmonic component, better electro magnetic computability, and lower switching losses. [2]

Multilevel inverter include an array of power semiconductors and capacitor voltage sources, the output of which generates voltages with stepped waveforms with less distortion, less switching frequency, higher efficiency, lower voltage devices and better electromagnetic compatibility[4]. The commutation of the switches permits the addition of the capacitor voltages, which reach high voltages at the output, while the power semiconductors must withstand only reduced voltage.

## II. (a). H – BRIDGE INVERTER

Another characteristic is that the "H" topology has many redundant combinations of switches' positions to produce the same voltage levels. As an example, the level "zero" can be generated with switches in position S(1) and S(2), or S(3) and S(4), or S(5) and S(6), and so on [7] [8] [9]. Another characteristic of "H" converters is that they only produce an odd number of levels, which ensures the existence of the "OV" level at the load .For example, a 51-level inverter using an "H" configuration with transistor-clamped topology requires 52 transistors, but only 25 power supplies instead of the 50 required when using a single leg [8]. Therefore, the problem related to increasing the number of levels and reducing the size and complexity has been partially solved, since power supplies have been reduced to 50%.

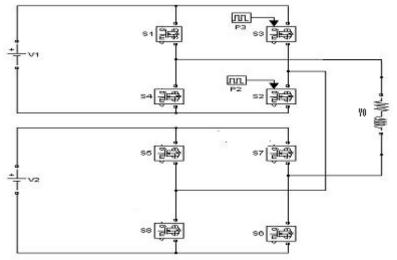

Figure.1.a shows the single-phase H – Bridge of cascaded inverter. The ac terminal voltages of each bridge are connected in series. Unlike the diode clamp or flying capacitors inverter, the cascaded inverter does not require any voltage-clamping diodes or voltage balancing capacitors. This configuration is useful for constant frequency applications such as active front-end rectifiers, active power filters, and reactive power compensation.

In this case, the power supply could also be voltage regulated dc capacitor. The circuit diagram consists of two cascade bridges. The load is connected in such a way that the sum of output of these bridges will appear across it. The ratio of the power supplies between the auxiliary bridge

and the main bridge is 1:3. One important characteristic of multilevel converters using voltage escalation is that electric power distribution and switching frequency present advantages for the implementation of these topologies. [9]

**Fig. 1.a**. H – Bridge Inverter

1

| Table 1: Switching Sequence of H – Bridge Inverter |           |           |           |           |           |           |           |  |  |

|----------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| Voltage<br>Level                                   | <i>S1</i> | <i>S2</i> | <i>S3</i> | <i>S4</i> | <i>S5</i> | <i>S6</i> | <i>S7</i> |  |  |

| -4Vdc                                              | 0         | 0         | 1         | 1         | 0         | 0         | 1         |  |  |

| -3Vdc                                              | 0         | 0         | 1         | 1         | 0         | 0         | 0         |  |  |

| -2Vdc                                              | 0         | 0         | 1         | 1         | 1         | 1         | 0         |  |  |

| -1Vdc                                              | 0         | 0         | 0         | 0         | 0         | 0         | 1         |  |  |

| 0                                                  | 0         | 0         | 0         | 0         | 0         | 0         | 0         |  |  |

| +1Vdc                                              | 0         | 0         | 0         | 0         | 1         | 1         | 0         |  |  |

| +2Vdc                                              | 1         | 1         | 0         | 0         | 0         | 0         | 1         |  |  |

| +3Vdc                                              | 1         | 1         | 0         | 0         | 0         | 0         | 0         |  |  |

0

1

+4Vdc

Using H-Bridge inverter the harmonics was reduced in 3 and 7 level output voltages. The inverter generates a high quality output voltage waveform. It reduces dv/dt stress imposed on power switching devices and also harmonic components of output voltage and load current quite well.

0

1

The phase output voltage is synthesized by the sum of two inverter outputs. Each inverter bridge is capable of generating three different levels of voltage outputs. The main bridge can generate +3Vdc, 0, -3Vdc and the auxiliary bridge can generate +Vdc, 0, -Vdc. By using appropriate combinations of switching devices many voltage levels are obtained. When the positive group switches are turned on the voltage across that particular bridge is positive. When the negative group switches are turned on the voltage across that particular bridge is negative. When S1, S2 are turned on the voltage across the main bridge is +3Vdc.

When S3, S4 are turned on the voltage across the main bridge is - 3Vdc. When S5, S6 are turned on the voltage across the auxiliary bridge is +Vdc. When S7, S8 are turned on the voltage across the auxiliary bridge is -Vdc. To obtain +2Vdc the switch combinations S1, S2, S7 & S8 are turned on. To obtain +4Vdc the switch combinations S1, S2, S5 & S6 are turned on. To obtain -2Vdc the switch combinations S3, S4, S5 & S6 are turned on. To obtain -4Vdc the switch combinations S3, S4, S7 & S8 are turned on. The table.1 shows the switching strategy of

0

0

transistors at each level. The status of the switch is '0', that switch is in OFF condition. The status of the switch is '1', that switch is in ON condition.

#### (b). Harmonic Reduction:

To eliminate 5<sup>th</sup>, 7<sup>th</sup>, and 9<sup>th</sup> order harmonics, the firing angles for each level is found by solving the following equations.

Cos 5a1 + Cos 5a2 + Cos 5a3 + Cos 5a4 = 0Cos 7a1 + Cos 7a2 + Cos 7a3 + Cos 7a4 = 0Cos 9a1 + Cos 9a2 + Cos 9a3 + Cos 9a4 = 0

Using Math CAD, the values of the "a" is obtained as follows a1 = 12.834 a2 = 29.908 a3 = 50.993 a4 = 64.229Where a1, a2, a3, a4 are the firing angles in degrees.

The switching pulses are obtained by carrying out the above calculation.

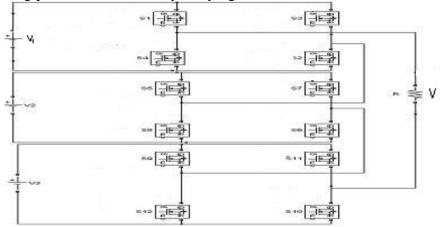

Fig. 2.a. H – Bridge 7 – Level Conventional Inverter

The H-Bridge 7-level conventional inverter is shown in the figure 2.a. The conventional 7- level inverter has some disadvantages they are requires 2(m-1) switching devices; increase the cost; large in size; controlling is complex. In order to over come the above draw backs the following model has been proposed.

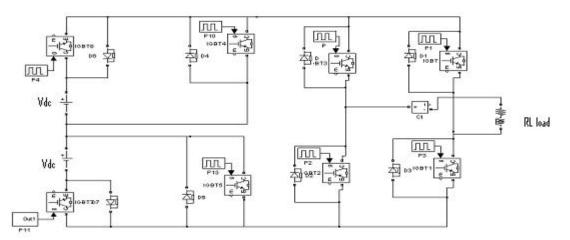

Fig. 3.a Proposed H – bridge 7 level inverter

The figure 3.a shows the proposed 7-level inverter. The proposed inverter generates a high quality output voltage waveform. It reduces dv/dt stress imposed on power switching devices. The table.2 shows the switching strategy of proposed H-bridge 7-level inverter at each level.

| ON                    | NODE A VOLTAGE  | NODE B VOLTAGE  | <b>OUTPUT VOLTAGES</b>    |

|-----------------------|-----------------|-----------------|---------------------------|

| SWITCHES              | $(V_A)$         | $(V_B)$         | $(V_{AB})$                |

| $Q_3, Q_4$            | 0               | 0               | 0                         |

| $Q_1, Q_4, Q_5$       | $V_d$           | 0               | $V_d$                     |

| $Q_1, Q_4, Q_7$       | $2V_d$          | 0               | $2V_d$                    |

| $Q_1, Q_4, Q_5, Q_7$  | 3V <sub>d</sub> | 0               | $3V_d$                    |

| $Q_1, Q_4, Q_7$       | $2V_d$          | 0               | $2V_d$                    |

| $Q_1, Q_4, Q_5$       | V <sub>d</sub>  | 0               | $\mathbf{V}_{\mathrm{d}}$ |

| Q1,Q2                 | 0               | 0               | 0                         |

| $Q_2, Q_3, Q_5$       | 0               | $V_d$           | -V <sub>d</sub>           |

| $Q_{2}, Q_{3}, Q_{7}$ | 0               | $2V_d$          | $-2V_d$                   |

| $Q_2, Q_3, Q_5, Q_7$  | 0               | 3V <sub>d</sub> | -3V <sub>d</sub>          |

| Q2,Q3,Q7              | 0               | $2V_d$          | -2V <sub>d</sub>          |

| Q2,Q3,Q5              | 0               | $V_d$           | -V <sub>d</sub>           |

**Table – 2:** Switching Sequence and Output Voltages Levels of Proposed seven level H – bridge Inverter

### (c). Simulation Results of H – Bridge Inverter:

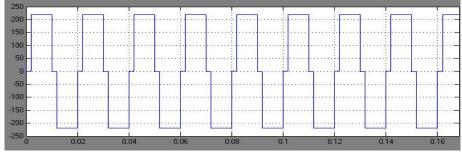

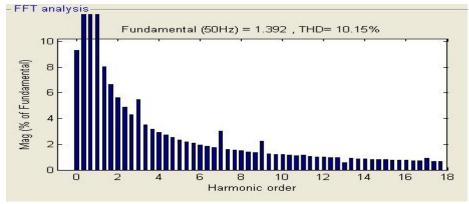

H - bridge three level inverter simulink circuit shown in fig 1.b. The output of the H - bridge inverter is connected with inductive load. The H - bridge inverter converts the DC voltage into AC voltage in various steps. The switching strategy of the circuit has explained in the previous section. This circuit is stimulated in MATLAB and the output wave form and harmonics by FFT analysis is obtained. The output waveform is shown in the figure 1.c. Fig 1.d shows the harmonics represent in the output THD value is 10.15 %.

Fig. 1.b. Simulink Circuit for H – Bridge – 3 level inverter

Fig. 1.c. H – Bridge – 3 level inverter output voltage

fig. 1. d. H – Bridge – 3 level inverter FFT analysis

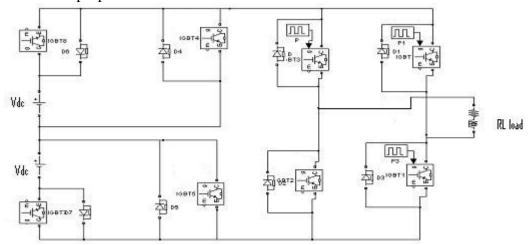

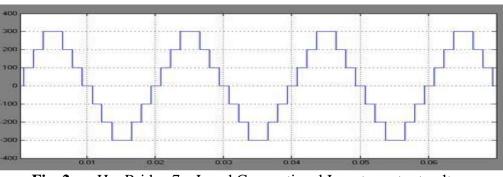

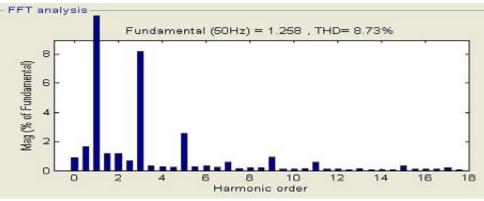

Conventional H – bridge three level inverter simulink circuit shown in fig 2.b. The output of the conventional H – bridge inverter is connected with inductive load. The Conventional H – bridge inverter converts the DC voltage into AC voltage in various steps. The switching strategy of the circuit has explained in the previous section. This circuit is stimulated in MATLAB and the output wave form and harmonics by FFT analysis is obtained. The output waveform is shown in the figure 2.c. Fig 2.d shows the harmonics represent in the output THD value 8.73%.

Fig. 2. b. H – Bridge 7 – Level Conventional Inverter

Fig. 2. c. H – Bridge 7 – Level Conventional Inverter output voltage

Fig. 2. d. H – Bridge 7 – Level Conventional Inverter FFT analysis

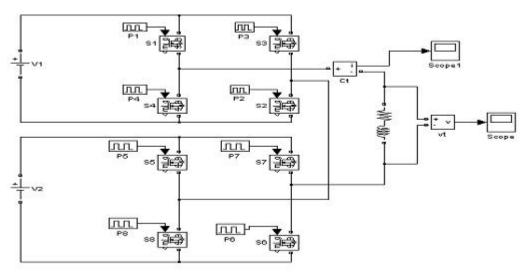

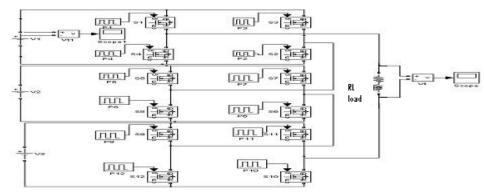

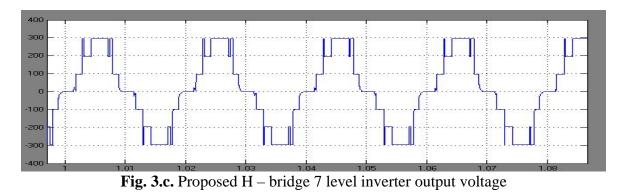

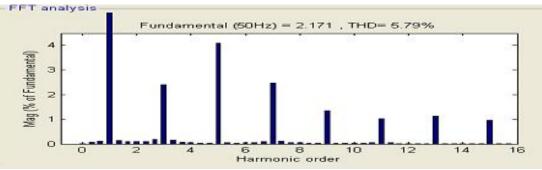

Proposed H – bridge three level inverter simulink circuit shown in fig 3.b. The output of the proposed H – bridge inverter is connected with inductive load. The proposed H – bridge inverter converts the DC voltage into AC voltage in various steps. The switching strategy of the circuit has explained in the previous section. This circuit is stimulated in MATLAB and the output wave form and harmonics by FFT analysis is obtained. The output waveform is shown in the figure 3.c. Fig 3.d shows the harmonics represent in the output THD value 5.79 %.

It can be found from the table 3 that with the use of H-Bridge three level inverter, there is a drastic decrease in the %THD level to 10.15%. Further with the use of H-Bridge seven level inverter and nine level inverter the %THD are 8.73% and 7.30% respectively. While using the proposed model the %THD level is reduce to 5.79%. This shows an improved performance of the H-bridge inverter.

Fig. 3.b. Simulink circuit for Proposed H – bridge 7 level inverter

Fig. 3.d. Proposed H – bridge 7 level inverter FFT analysis

#### Table – 3: Comparison of harmonics in multilevel inverter

| TYPE OF INVERTER                         | THD HARMONICS (%) |

|------------------------------------------|-------------------|

| H – Bridge Three Level Inverter          | 10.15 %           |

| H – Bridge Seven Level Inverter          | 8.73 %            |

| H – Bridge Proposed Seven Level Inverter | 5.79 %            |

#### CONCLUSION

H - bridge inverter has been analysised and simulated with reduced harmonics. Finally the harmonics in multilevel inverter at different stages were compared. From that comparison, it can be seen that the seven level inverter has least value of THD.

#### REFERENCES

- 1. John N. Chiasson, Leon M. Tolbert, Keith J. McKenzie, Zhong Du, " A Complete solution to the harmonic elimination problem", IEEE transactions on power electronics, Vol. 19, No.2, pp. 491-498, March 2004.

- 2. Jose Rodriguez, Jin-Sheng Lai and Fang Zheng, "Multilevel Inverters: A survey of topologies, Control applications," IEEE transactions on Industrial Electronics, Vol.49, No. 4, pp. 724-738, August 2002.

- 3. V. G. Agelidis and M. Calais, "Application specific harmonic performance evaluation of multicarrier PWM techniques," in proc. IEEE PESC'98, vol. 1, 1998, pp. 172 178.

- 4. A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter, "IEEE Trans. Ind. Applicat., vol. IA 17, pp. 518 523, Sept./Oct. 1981.

- 5. P. D. Ziogas, "Optimum voltage and harmonic control PWM techniques for three-phase static UPS inverters," IEEE Trans. Ind. Applicat., vol. IA-16. no. 4, pp. 542-546, July/Aug. 1980.

- H. Patel and R. G. Hoft, "Generalized techniques of harmonic elimination and voltage control in thyristors: Part – I Harmonics elimination," IEEE Trans. Ind. Applicat., vol. IA-9, no. 3, pp. 310-317, May/June 1974.

- E. Babaei, S. H. Hosseini, G. B. Gharehpetian, M. T. Haque, and M. Sabahi, "Reduction of dc voltage sources and switches in asymmetrical multilevel converters using a novel topology," *Elsevier J. Electr. Power Syst. Res.*, vol. 77, no. 8, pp. 1073–1085, Jun. 2007.

- 8. M. Manjrekar, P. K. Steimer, and T. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high-power applications," *IEEE Trans. Ind. Appl.*, vol. 36, no. 3, pp. 834–841, May/Jun. 2000.

- 9. Z. Du, L. M. Tolbert, J. N. Chiasson, and B. Ozpineci, "A cascade multi-level inverter using a single dc power source," in *Proc. IEEE APEC*, 2006, pp. 426–430.